# TERNARY MAX-MIN ALGEBRA WITH APPLICATION TO REVERSIBLE LOGIC SYNTHESIS

# MUSHARRAT KHAN Bachelor of Science, East West University, Bangladesh, 2014

A Thesis

Submitted to the School of Graduate Studies

of the University of Lethbridge

in Partial Fulfillment of the

Requirements for the Degree

## MASTER OF SCIENCE

Department of Mathematics and Computer Science University of Lethbridge LETHBRIDGE, ALBERTA, CANADA

© Musharrat Khan, 2017

# TERNARY MAX-MIN ALGEBRA WITH APPLICATION TO REVERSIBLE LOGIC SYNTHESIS

## MUSHARRAT KHAN

Date of Defence: March 15, 2017

Dr. Jacqueline E. Rice

Supervisor Professor Ph.D.

Dr. Howard Cheng

Committee Member Associate Professor Ph.D.

Dr. Locke Spencer

Committee Member Assistant Professor Ph.D.

Dr. Amir Akbary-Majdabadno

Chair, Thesis Examination Com- Professor Ph.D.

mittee

# **Dedication**

To them who advance reversible computing.

## **Abstract**

Ternary reversible circuits are 0.63 times more compact than equivalent binary reversible circuits and are suitable for low-power implementations. Two notable previous works on ternary reversible circuit synthesis are the ternary Galois field sum of products (TGFSOP) expression-based method and the ternary Max-Min algebra-based method. These methods require high quantum cost and large number of ancilla inputs. To address these problems we develop an alternative ternary Max-Min algebra-based method, where ternary logic functions are represented as Max-Min expressions and realized using our proposed multiple-controlled unary gates. We also show realizations of multiple-controlled unary gates using elementary quantum gates. We develop a method for minimization of ternary Max-Min expressions of up to four variables using ternary K-maps. Finally, we develop a hybrid Genetic Algorithm (HGA)-based method for the synthesis of ternary reversible circuits. The HGA has been tested with 24 ternary benchmark functions with up to five variables. On average our method reduces quantum cost by 41.36% and requires 35.72% fewer ancilla inputs than the TGFSOP-based method. Our method also requires 74.39% fewer ancilla inputs than the previous ternary Max-Min algebra-based method.

## Acknowledgments

I would like to express my heartfelt thanks and gratitude to my thesis supervisor Dr. Jacqueline E. Rice for her tireless effort for managing funds for my study, for continuous advice, encouragement, and guidance for both course work and research work, and most importantly for standing beside me during my academic and personal odds, without which this thesis would have not seen the day light. Simply saying thanks to her will be inadequate for what she has done for me.

I would also like to thank my committee members Dr. Howard Cheng and Dr. Locke Spencer for their encouragement and suggestions for improving the quality of my thesis. I specially thank Dr. Howard Cheng for his academic and administrative helps.

I must thank Administrative Support Ms. Barb Hodgson for her cordial support whenever I needed help from her.

I would like to thank anonymous reviewers of my two conference papers published in *Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, Montreal, Canada, May 2016 for their invaluable suggestions to improve my papers that constitute a large part of my thesis.

I also thank other faculty members of the department and my fellow students for their unconditional helps and supports.

Finally, I must thank my parents for extending every possible supports and absorbing emotional pains to keep their only daughter alone staying several thousand miles away from home for this study.

This list is not an exhaustive list to thank. Anybody who directly or indirectly helped me in any aspect during my study also deserves a great thank.

# **Contents**

| Co | Contents |                                                                       |    |  |

|----|----------|-----------------------------------------------------------------------|----|--|

| Li | st of T  | ables                                                                 | ix |  |

| Li | st of I  | ligures                                                               | xi |  |

| 1  | Intr     | oduction                                                              | 1  |  |

|    | 1.1      | Motivation of the Thesis                                              | 1  |  |

|    | 1.2      | Outcomes of the Thesis                                                | 3  |  |

|    | 1.3      | Organization of the Thesis                                            | 4  |  |

| 2  | Bacl     | ground                                                                | 6  |  |

|    | 2.1      | Introduction                                                          | 6  |  |

|    | 2.2      | Reed-Muller Representations of Binary Logic Functions                 | 7  |  |

|    | 2.3      | Ternary Logic                                                         | 10 |  |

|    |          | 2.3.1 Advantages of Ternary Logic                                     | 11 |  |

|    |          | 2.3.2 Disadvantages of Ternary Logic                                  | 11 |  |

|    | 2.4      | Max-Min Algebra-Based Representation of Ternary Logic Functions       | 12 |  |

|    |          | 2.4.1 Ternary Max-Min Algebra                                         | 12 |  |

|    |          | 2.4.2 Ternary Max-Min Expression                                      | 13 |  |

|    |          | 2.4.3 Ternary Logic Function Representation Using Max-Min Expressions | 15 |  |

|    | 2.5      | Galois Field-Based Representation of Ternary Logic Functions          | 16 |  |

|    |          | 2.5.1 Ternary Galois Field                                            | 16 |  |

|    |          | 2.5.2 Ternary Galois Field Sum of Products (TGFSOP) Expressions       | 18 |  |

|    | 2.6      | Ternary Karnaugh Map                                                  | 18 |  |

|    |          | 2.6.1 Structures of Ternary K-Maps                                    | 19 |  |

|    |          | 2.6.2 Putting Ternary Logic Functions on a Ternary K-Map              | 19 |  |

|    | 2.7      | Reversible Logic                                                      | 21 |  |

|    |          | 2.7.1 Irreversible Logic Versus Reversible Logic                      | 21 |  |

|    |          | 2.7.2 Advantages of Reversible Logic Over Irreversible Logic          | 23 |  |

|    |          | 2.7.3 Disadvantages of Reversible Logic                               | 24 |  |

|    | 2.8      | Ternary Reversible Logic                                              | 25 |  |

|    |          | 2.8.1 Ternary Reversible Gates                                        | 25 |  |

|    |          | 2.8.2 Realizations of TGFSOP Expressions Using Feynman and Toffoli    |    |  |

|    |          | Gates                                                                 | 27 |  |

|    | 2.9      | Reversible Circuit Realization Complexities                           | 28 |  |

| 3 | Lite | rature Review                                                            | <b>30</b> |

|---|------|--------------------------------------------------------------------------|-----------|

|   | 3.1  | Introduction                                                             | 30        |

|   | 3.2  | Realizations of Macro-Level Ternary Reversible Gates                     | 30        |

|   | 3.3  | Previous Works on Reversible Synthesis of Ternary Logic Circuits         | 33        |

|   |      | 3.3.1 Genetic Algorithm-Based Synthesis of Ternary Reversible Circuits . | 33        |

|   |      | 3.3.2 Max-Min Algebra-Based Synthesis of Ternary Reversible Circuits .   | 34        |

|   |      | 3.3.3 Transformation-Based Synthesis of Ternary Reversible Circuits      | 36        |

|   |      | · · · · · · · · · · · · · · · · · · ·                                    | 37        |

|   |      | , , , , , , , , , , , , , , , , , , ,                                    | 40        |

|   |      | J 1                                                                      | 41        |

| 4 | Terr | nary Logic Function Representation Using Max-Min Algebra                 | 42        |

|   | 4.1  | Introduction                                                             | 42        |

|   | 4.2  |                                                                          | 43        |

|   | 4.3  | Ternary Logic Function Representation using Max-Min Algebra              | 44        |

|   |      | 4.3.1 Sub-Functions of a Ternary Logic Function                          | 44        |

|   |      | 4.3.2 Canonical Max-Min Expression for a Sub-Function                    | 45        |

| 5 | Terr | nary Multiple-Controlled Unary Gates                                     | 48        |

|   | 5.1  | Introduction                                                             | 48        |

|   | 5.2  | Ternary Elementary Quantum Gates                                         | 49        |

|   | 5.3  | Ternary Single-Controlled Unary Gates                                    | 49        |

|   |      | 5.3.1 Ternary Single-Controlled Unary Gates with Simple Control          | 49        |

|   |      | 5.3.2 Ternary Single-Controlled Unary Gates with Composite Control       | 50        |

|   |      | 5.3.3 Realization Complexities of Ternary Single-Controlled Unary Gates  | 51        |

|   | 5.4  | Ternary Multiple-Controlled Unary Gates                                  | 52        |

|   |      | 5.4.1 Ternary Multiple-Controlled Unary Gates with Simple Controls       | 52        |

|   |      | 5.4.2 Ternary Multiple-Controlled Unary Gates with Composite Controls    | 54        |

|   |      | 5.4.3 Ternary Multiple-Controlled Unary Gates with Mixed Controls        | 56        |

|   |      | 5.4.4 Realization Complexities of Multiple-Controlled Unary Gates        | 57        |

| 6 | Terr | nary Reversible Circuit Synthesis Using Max-Min Algebra                  | 59        |

|   | 6.1  | Introduction                                                             | 59        |

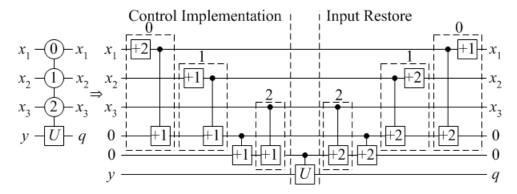

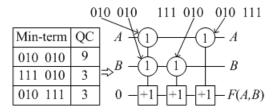

|   | 6.2  | Mapping of Ternary Max-Min Expressions into Reversible Circuits          | 60        |

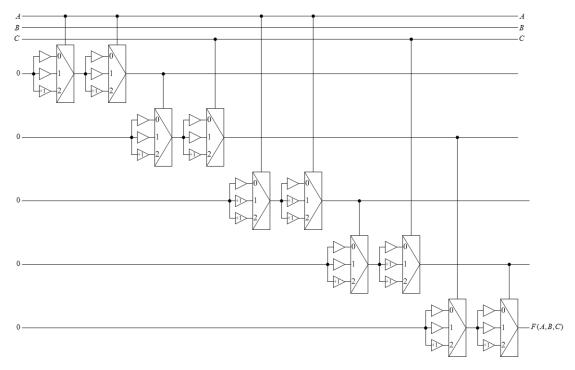

|   | 6.3  | Architectures of Ternary Reversible Circuit Synthesis                    | 63        |

|   | 6.4  | Ternary Reversible Circuit Synthesis Example                             | 66        |

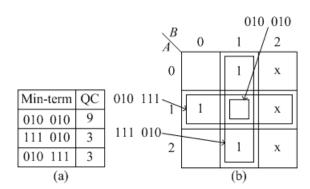

|   | 6.5  | Post Synthesis Quantum Cost Reduction                                    | 66        |

| 7 | Terr | nary K-map-Based Minimization of Ternary Max-Min Expressions             | 69        |

|   | 7.1  | Introduction                                                             | 69        |

|   | 7.2  | Motivation of Minimization of Ternary Max-Min Expressions                | 70        |

|   | 7.3  |                                                                          | 72        |

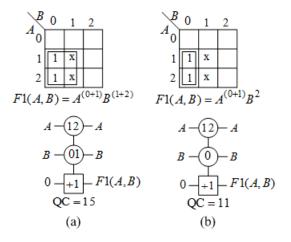

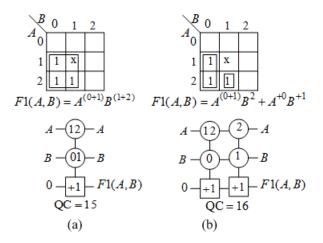

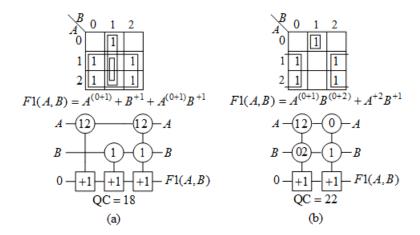

|   |      | 1 0                                                                      | 72        |

|   |      |                                                                          | 74        |

|          | 7.4    | Minimization of Ternary Max-Min Expression of a Ternary Sub-Function    |     |

|----------|--------|-------------------------------------------------------------------------|-----|

|          |        | Using Ternary K-Map                                                     | 75  |

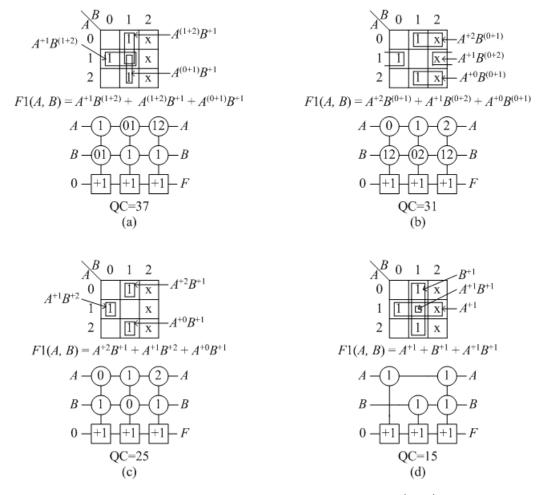

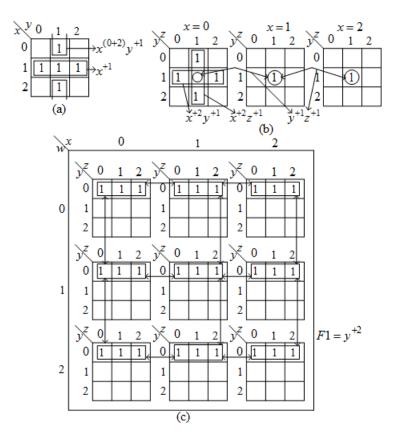

|          |        | 7.4.1 Grouping and Determining Max-Min Expression                       | 75  |

|          |        | 7.4.2 Some Observations                                                 | 78  |

|          |        | 7.4.3 K-Map-Based Minimization Method                                   | 83  |

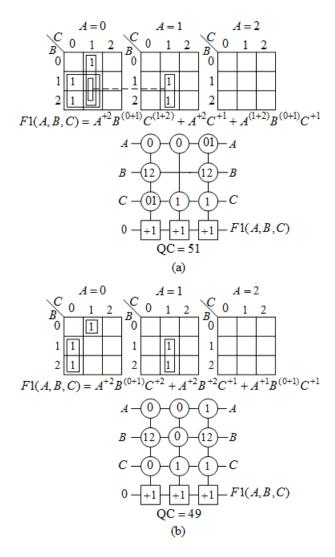

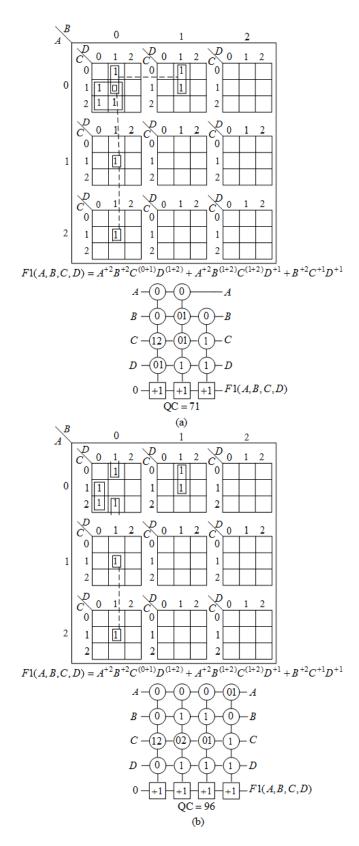

|          | 7.5    | Ternary K-Map-Based Minimization Examples                               | 84  |

|          | 7.6    | Comparison Between K-Map-Based ESOP and Ternary Max-Min Mini-           |     |

|          |        | mizations                                                               | 88  |

| 8        | Hyb    | rid Genetic Algorithm-Based Synthesis of Ternary Reversible Circuits Us | -   |

|          | ing N  | Max-Min Algebra                                                         | 90  |

|          | 8.1    | Introduction                                                            |     |

|          | 8.2    | Brief Introduction to Genetic Algorithms (GAs)                          |     |

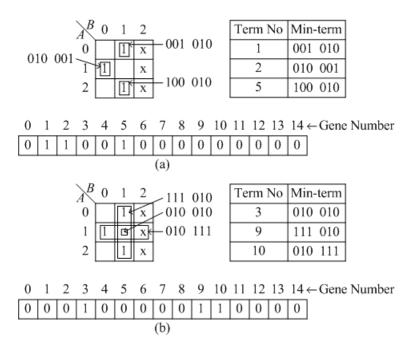

|          | 8.3    | Generation of Potential Candidate Minterms for Solution                 | 96  |

|          |        | 8.3.1 Encoding of Variable Value Variation                              | 96  |

|          |        | 8.3.2 Minterm Generation                                                | 98  |

|          |        | 8.3.3 Reducing the Number of Potential Minterms                         | 99  |

|          |        | 8.3.4 Example of Minterm Generation                                     | 100 |

|          |        | 8.3.5 Algorithm for Minterm Generation                                  | 101 |

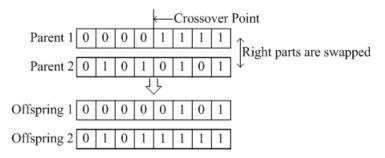

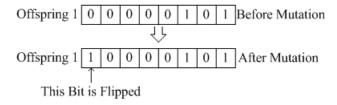

|          | 8.4    | Problem Encoding into Genetic Algorithm Domain                          | 103 |

|          | 8.5    | Proposed Hybrid Genetic Algorithm (HGA)                                 | 105 |

|          | 8.6    | Ternary Reversible Circuit Synthesis From Outputs of Hybrid Genetic Al- |     |

|          |        | gorithm                                                                 | 111 |

|          |        | 8.6.1 Logic-Level Ternary Circuit Synthesis Using Multiple-Controlled   |     |

|          |        | Unary Gates from Output of the Hybrid Genetic Algorithm                 | 111 |

|          |        | 8.6.2 Post Synthesis Quantum Cost Reduction                             | 112 |

| 9        | Expe   | erimental Results                                                       | 115 |

|          | 9.1    | Introduction                                                            | 115 |

|          | 9.2    | Results of Ternary Benchmark Sub-Function Synthesis Using Hybrid Ge-    |     |

|          |        | netic Algorithm (HGA)                                                   |     |

|          | 9.3    | Results of Ternary Benchmark Circuit Synthesis                          | 121 |

|          | 9.4    | Comparison of Circuit Synthesis Results With Previous Work              | 122 |

| 10       |        | clusion and Future Work                                                 | 126 |

|          | 10.1   | Conclusion                                                              | 126 |

|          | 10.2   | Future Work                                                             | 127 |

| Bil      | bliogr | aphy                                                                    | 130 |

| <b>A</b> | Torr   | ary Ponchmark Functions                                                 | 122 |

# **List of Tables**

| An example 4-variable binary logic function.                                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ternary Max operation                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ternary Min operation                                                       | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ternary Complement (or Negation) operation                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1-Reduced Post literals of a variable                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-Reduced Post literals of a variable                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Truth table of a ternary half-adder                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GF3 addition operation                                                      | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GF3 multiplication operation                                                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An example two-variable ternary logic function                              | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Truth table of the binary EXOR function                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Truth table of the binary reversible EXOR function                          | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ternary single-input (unary) reversible operations and their corresponding  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| reversible literals                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Comment France of 1 De level De d'Armile                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Compound Forms of 1-Reduced Post Interals                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ternary unary reversible operations and their corresponding literals        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| , ,                                                                         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <u> </u>                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| minterm for an input combination                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| unary gate realizations                                                     | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An example two-variable ternary logic function and its three sub-functions  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <u> </u>                                                                    | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

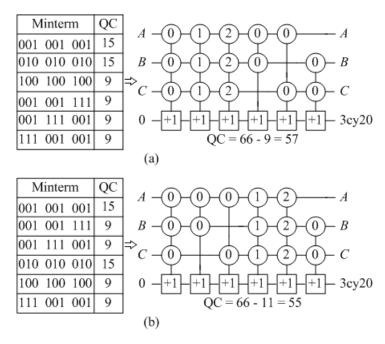

| 1                                                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 ost symmetris quantum cost reduction.                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| An example two-variable ternary logic function and its three sub-functions. | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Truth table for a ternary full-adder with all sub-functions                 | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Variable value encoding in a group of cells                                 | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                             | 90<br>97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| • •                                                                         | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                             | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                             | Ternary Max operation.  Ternary Min operation.  Ternary Complement (or Negation) operation.  1-Reduced Post literals of a variable.  2-Reduced Post literals of a variable.  Truth table of a ternary half-adder.  GF3 addition operation.  GF3 multiplication operation.  An example two-variable ternary logic function.  Truth table of the binary EXOR function.  Truth table of the binary reversible EXOR function.  Truth table of the binary reversible example two-variable literals.  Compound Forms of 1-Reduced Post literals.  Ternary unary reversible operations and their corresponding literals.  Ternary unary non-reversible operations and their corresponding literals.  An example two-variable ternary logic function and its three sub-functions.  Reversible literal assignment to input values for determining the canonical minterm for an input combination.  Quantum costs and number of ancilla inputs for ternary single-controlled unary gate realizations.  An example two-variable ternary logic function and its three sub-functions.  Literal to control value mapping for realization of a minterm using a ternary multiple-controlled unary gate.  Post synthesis quantum cost reduction.  An example two-variable ternary logic function and its three sub-functions.  Truth table for a ternary full-adder with all sub-functions.  Variable value encoding in a group of cells.  An example two-variable ternary logic function and its three sub-functions.  Minterm generation for sub-function F1(A, B) in Table 8.2. |

| 8.5 | List of minterms which are potential candidates for optimal (or near opti- |

|-----|----------------------------------------------------------------------------|

|     | mal) solution                                                              |

| 8.6 | Experimental results of generic GA-based minimization of some ternary      |

|     | benchmark sub-functions from Appendix A                                    |

| 8.7 | Mapping of value change of a variable to literal and mapping of literal to |

|     | control value of the multiple-controlled unary gate                        |

| 9.1 | Experimental results of minterm generation and HGA-based synthesis of      |

|     | ternary reversible logic circuits                                          |

| 9.2 | Experimental results of minterm generation and HGA-based synthesis of      |

|     | ternary reversible logic circuits (continued)                              |

| 9.3 | Experimental results of minterm generation and HGA-based synthesis of      |

|     | ternary reversible logic circuits (continued)                              |

| 9.4 | Ternary reversible circuit realization results                             |

| 9.5 | Comparison of our Max-Min expression-based synthesis results with those    |

|     | of TGFSOP-based method [16]                                                |

| 9.6 | Comparison of number of ancilla inputs required in our method with those   |

|     | of [5]                                                                     |

# **List of Figures**

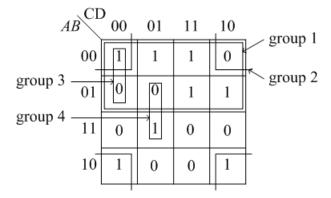

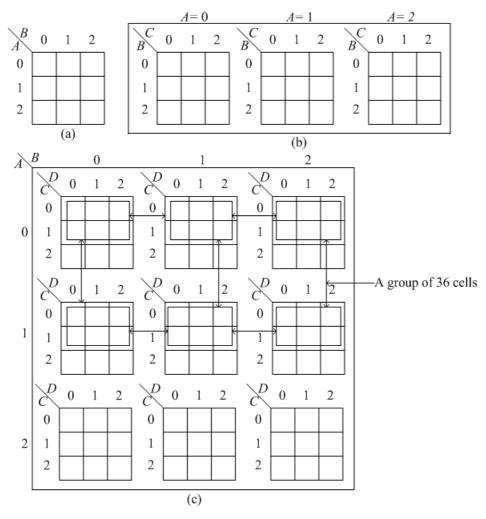

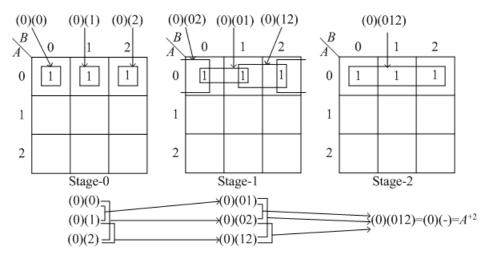

| 2.1 | ESOP minimization for the Boolean function in Table 2.1                                                                                         | 9   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

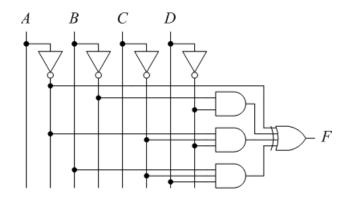

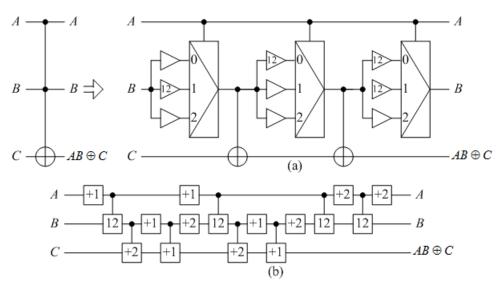

| 2.2 | Realization of the ESOP expression (2.1)                                                                                                        | 10  |

| 2.3 | Structures of (a) a two-variable, (b) a three-variable, and (c) a four-variable                                                                 |     |

|     | ternary K-map.                                                                                                                                  | 20  |

| 2.4 | Putting the ternary function $F(A,B)$ of Table 2.10 on a two-variable ternary                                                                   |     |

|     | K-map                                                                                                                                           | 21  |

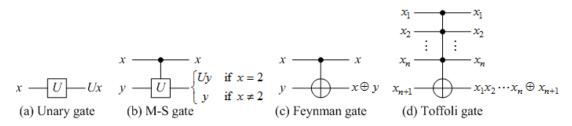

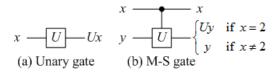

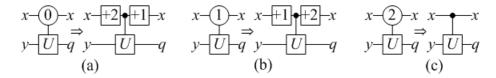

| 2.5 | Ternary reversible (a) unary, (b) M-S, (c) Feynman, and (d) Toffoli gates                                                                       | 25  |

| 2.6 | The family of generalized ternary gates (GTGs)                                                                                                  | 27  |

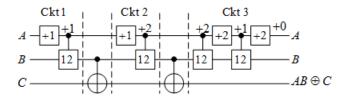

| 2.7 | Realization of the TGFSOP expression (2.6)                                                                                                      | 28  |

| 3.1 | Realization of generalized ternary gate (GTG) from [12]                                                                                         | 31  |

| 3.2 | Realization of ternary Feynman gate from [12]                                                                                                   | 32  |

| 3.3 | Realization of a three-input Tofoli gate from [12]. (a) Realization using                                                                       |     |

|     | GTGs and Feynman gates. (b) Realization after replacing the GTGs and                                                                            |     |

|     | the Feynman gates by their corresponding realizations using unary and M-                                                                        |     |

|     | S gates                                                                                                                                         | 32  |

| 3.4 | Realization of a ternary Feynman gate from [15]                                                                                                 | 33  |

| 3.5 | Realization of a three-input ternary Toffoli gate from [15]                                                                                     | 33  |

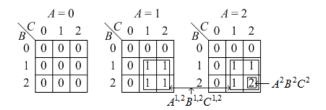

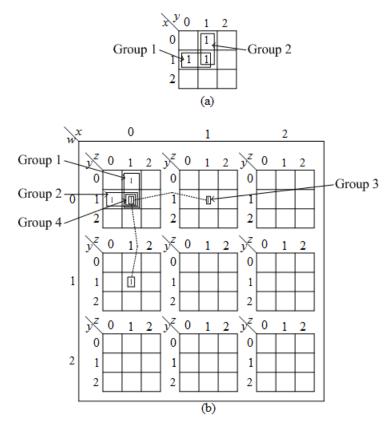

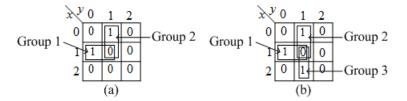

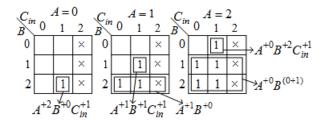

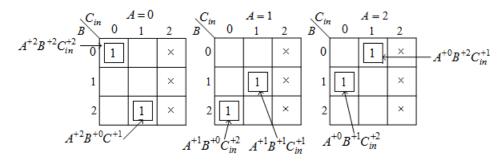

| 3.6 | K-map representing ternary $Min(A, B, C)$ function                                                                                              | 35  |

| 3.7 | GTG cascade for the expression (3.1)                                                                                                            | 36  |

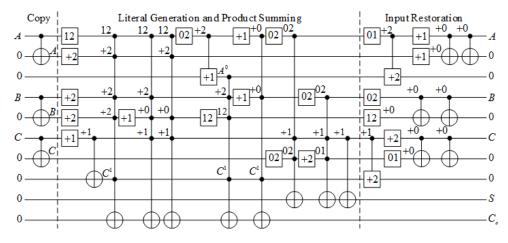

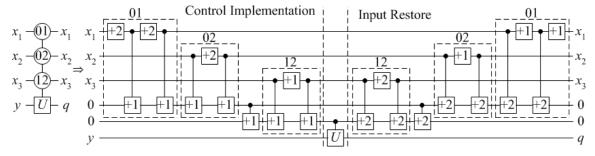

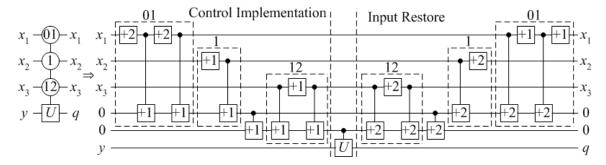

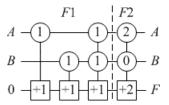

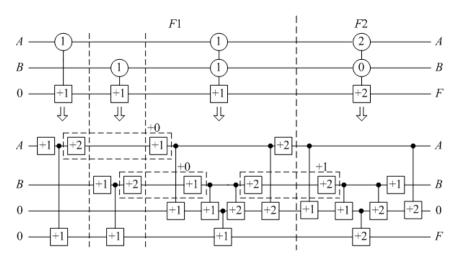

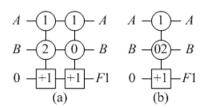

| 3.8 | Reversible realization of a ternary full-adder using the TGFSOP expressions (3.2) and (3.3) using a cascade of unary, M-S, Feynman, and Toffoli |     |

|     | gates from [16]                                                                                                                                 | 39  |